EPM7064STC100-7 CPLD: características, aplicaciones y guía de programación en el sistema

El EPM7064STC100-7 es un poderoso chip de la serie MAX® 7000S de Intel, diseñada para manejar tareas complejas en dispositivos electrónicos.Esta guía analiza las características y usos principales del EPM7064STC100-7, enfatizando su capacidad de ser reprogramado fácilmente, su operación rápida y su diseño flexible.Ideal para muchas tecnologías diferentes, desde pequeños dispositivos hasta grandes máquinas industriales, este chip es una pieza clave para construir circuitos digitales avanzados.Catalogar

EPM7064STC100-7 Descripción

El EPM7064STC100-7 es un complejo dispositivo lógico programable (CPLD) de la serie MAX® 7000S de Intel.Tiene 64 macrocellos y 1.250 puertas, que ayudan a construir circuitos digitales complejos.Este chip funciona a una velocidad máxima de 166.7 MHz, con un retraso de señal de 7.5 nanosegundos (NS).Tiene 68 pines de entrada/salida (E/S) que funcionan con una lógica de 3.3V y 5V, lo que facilita el uso en diferentes circuitos.Una característica clave es su programabilidad en el sistema de 5.0V (ISP) a través de una interfaz JTAG (IEEE 1149.1).Esto significa que puede reprogramarlo sin eliminarlo del circuito, facilitando las pruebas y las actualizaciones.Viene en un paquete plano cuádruple de 100 pines (TQFP), que es un paquete compacto de montaje en superficie.Este CPLD se utiliza en sistemas integrados, procesamiento de señales digitales, dispositivos de comunicación y automatización industrial.

Brindamos componentes de alta calidad y servicios personalizados, por lo que es mejor hacer su pedido a granel con nosotros para soluciones confiables de CPLD.

EPM7064STC100-7 Características

• Lógica de alta densidad: El EPM7064STC100-7 está diseñado con 64 macrocellos y 1.250 puertas utilizables, lo que lo hace muy adecuado para implementar funciones lógicas complejas en circuitos digitales.Esta arquitectura de alta densidad permite crear intrincados diseños lógicos al tiempo que mantiene la eficiencia en operaciones lógicas programables.La estructura de macrocelín bien optimizada garantiza una utilización efectiva de los recursos disponibles, admitiendo implementaciones lógicas combinacionales y secuenciales avanzadas.

• Rendimiento rápido: Construido para un procesamiento de alta velocidad, el EPM7064STC100-7 funciona con una frecuencia interna máxima de 166.7 MHz, lo que permite la ejecución rápida de funciones lógicas.Su retraso de propagación de 7.5 ns garantiza una latencia mínima.Esta capacidad de conmutación rápida mejora la capacidad del dispositivo para manejar el procesamiento de datos de alta velocidad, el acondicionamiento de la señal y controlar las tareas de manera eficiente, lo que lo convierte en una elección confiable para sistemas digitales exigentes.

• E/S versátil: Con 68 pines de entrada/salida programables, el EPM7064STC100-7 ofrece una flexibilidad excepcional para la integración en varios diseños de circuitos.Admitiendo niveles lógicos de 3.3V y 5V, permite una compatibilidad perfecta con diferentes voltajes del sistema, eliminando la necesidad de palancas de nivel de nivel de voltaje adicionales.Esta adaptabilidad lo hace bien adecuado para aplicaciones en entornos de voltaje mixto, asegurando una amplia aplicabilidad entre sistemas integrados, controles industriales y redes de comunicación.

• Programabilidad en el sistema (ISP): Una de las ventajas de la EPM7064STC100-7 es su programabilidad del sistema (ISP) de 5.0V, facilitada a través de una ETS IEEE.1149.1 interfaz JTAG.Esta característica permite reprogramar y modificar las funciones lógicas sin desarmar ni eliminar físicamente el dispositivo, simplificando el mantenimiento, la depuración y el desarrollo iterativo.La capacidad del ISP reduce el tiempo de inactividad y mejora la flexibilidad de las actualizaciones de firmware, lo que la hace invaluable para diseños digitales dinámicos y reconfigurables.

EPM7064STC100-7 Modelos CAD

Símbolo EPM7064STC100-7

EPM7064STC100-7 Huella

EPM7064STC100-7 Modelo 3D

EPM7064STC100-7 Diagrama de bloques

El EPM7064STC100-7 Diagrama de bloques Muestra cómo se conectan y controlan los elementos lógicos del chip.Tiene cuatro bloques de matriz lógica (laboratorios), etiquetados como A, B, C y D, cada uno que contiene 16 macrocellos.Estas macrocellos realizan funciones lógicas y se conectan a través de una matriz de interconexión programable (PIA), que permite un enrutamiento flexible de las señales.Cada laboratorio está vinculado a un bloque de control de E/S, que maneja hasta 16 pines de entrada/salida por laboratorio.El diagrama también muestra señales de control globales (GCLK1, GCLK2, OE1 y GCLRN) que ayudan a administrar las funciones de marcado y restablecimiento del chip.Algunas puertas lógicas procesan estas señales antes de llegar a diferentes partes del sistema.El diseño del EPM7064STC100-7 le permite utilizar en varias aplicaciones lógicas programables, como máquinas de estado, decodificación de direcciones y otros circuitos digitales personalizados.Sus interconexiones flexibles aseguran un flujo de señal eficiente y una operación confiable.

EPM7064STC100-7 Especificaciones

|

Tipo |

Parámetro |

|

Fabricante |

Altera/Intel |

|

Serie |

Max® 7000S |

|

Embalaje |

Bandeja |

|

Estatus de parte |

Obsoleto |

|

Tipo programable |

En el sistema programable |

|

Tiempo de retraso TPD (1) Max |

7.5 ns |

|

Suministro de voltaje - interno |

4.75V ~ 5.25V |

|

Número de elementos lógicos/bloques |

4 |

|

Número de macrocélulas |

64 |

|

Número de puertas |

1250 |

|

Número de E/S |

68 |

|

Temperatura de funcionamiento |

0 ° C ~ 70 ° C (TA) |

|

Tipo de montaje |

Montaje en superficie |

|

Paquete / estuche |

100-tqfp |

|

Paquete de dispositivos de proveedor |

100-TQFP (14x14) |

|

Número de producto base |

EPM7064 |

EPM7064STC100-7 Secuencia de programación en el sistema (ISP)

El EPM7064STC100-7, una parte de la familia CPLD Max 7000S, sigue una secuencia de programación en el sistema de seis etapas (ISP) para garantizar la configuración correcta.Este proceso le permite programar el dispositivo sin eliminarlo de la placa de circuito.El proceso de ISP implica las instrucciones, direcciones y datos de cambio a través del PIN de TDI (datos de prueba) mientras recupera las respuestas a través del PIN TDO (Data de prueba).

La primera etapa, Ingrese ISP, asegura que los pines de E/S pasen sin problemas del modo de usuario al modo ISP y requieran aproximadamente 1 m.Esto es seguido por Comprobar la identificación, donde se lee la ID de silicio del dispositivo para confirmar el objetivo correcto.A continuación, el Borrar a granel Cambios en la etapa en las instrucciones de borrado y aplica un pulso de borrado de 100 ms, eliminando todos los datos existentes en las células EEPROM.El Programa Sigue la etapa, donde las direcciones y los datos se cambian secuencialmente al dispositivo, aplicando pulsos de programación para configurar las celdas EEPROM.Cada dirección debe programarse individualmente, lo que hace que este paso consiga el tiempo dependiendo del número de células EEPROM en el dispositivo.

Una vez que se completa la programación, el Verificar La etapa asegura que los datos se hayan almacenado correctamente.Aquí, los pulsos de lectura se aplican a las células EEPROM, y los datos recuperados se comparan con los valores esperados.Si se encuentran discrepancias, la reprogramación puede ser necesaria.Finalmente, el Salir ISP La etapa asegura que la transición de PIN de E/S vuelva al modo de usuario, que requiere otros 1 ms.El tiempo total de programación o verificación está influenciado por dos factores principales: tiempo de pulso, requerido para borrar EEPROM, programación y operaciones de lectura, y tiempo de cambio, que depende de la frecuencia TCK (reloj de prueba) y el número de ciclos necesarios para transferir instrucciones, direcciones y datos.Dado que diferentes dispositivos con capacidad de ISP tienen un número variable de células EEPROM, tanto los tiempos totales y variables totales son exclusivos de cada dispositivo.El tiempo total del ISP se puede calcular en función de la frecuencia TCK, el número de dispositivos objetivo y la arquitectura EEPROM.

Aplicaciones EPM7064STC100-7

Sistemas integrados

El EPM7064STC100-7 se usa ampliamente en aplicaciones de sistemas integrados, donde sirve como una solución lógica programable flexible para controlar varios periféricos, señales de procesamiento e implementar protocolos personalizados.Su capacidad para interactuar con microcontroladores y sensores permite optimizar el rendimiento del sistema mientras se mantiene una huella compacta.Con su operación de alta velocidad y su bajo consumo de energía, es una excelente opción para aplicaciones integradas que requieren confiabilidad y eficiencia.

Procesamiento de señal digital (DSP)

En el procesamiento de señales digitales, el EPM7064STC100-7 juega un papel en la implementación de filtros, modulación de señal y varias funciones matemáticas.Sus rápidas velocidades de conmutación y su bajo retraso de propagación lo hacen adecuado para manejar tareas de procesamiento de datos de alta frecuencia, asegurando una latencia mínima en la conversión y manipulación de la señal.Se usa comúnmente en procesamiento de audio, telecomunicaciones y sistemas de radar.

Comunicaciones de datos

El EPM7064STC100-7 se utiliza ampliamente en sistemas de redes y comunicación de datos debido a su capacidad para manejar operaciones lógicas intensivas como enrutamiento de datos, almacenamiento en búfer y corrección de errores.Sus capacidades programables de E/S le permiten adaptarse a diferentes protocolos de comunicación, por lo que es un componente valioso en los interruptores, enrutadores e infraestructura de telecomunicaciones de Ethernet.Su soporte para la programabilidad del sistema (ISP) también permite actualizaciones de campo, mejorando la adaptabilidad en entornos de red dinámicos.

Automatización industrial

Las aplicaciones industriales exigen alta confiabilidad, durabilidad y bajo consumo de energía, lo que hace que el EPM7064STC100-7 sea una opción preferida para controladores lógicos programables (PLC), sistemas de control de motor y equipos de prueba automatizados.Con su programabilidad en el sistema basada en JTAG, proporciona la capacidad de refinar los procesos de automatización sin requerir la eliminación física o el rediseño.Su versatilidad en la compatibilidad de voltaje también lo hace adecuado para la interfaz con una amplia gama de sensores y actuadores utilizados en entornos industriales.

EPM7064STC100-7 piezas similares

EPM7064STC100-7 Ventajas

Programabilidad en el sistema (ISP)

Una de las mayores ventajas del EPM7064STC100-7 es su capacidad de ser reprogramado mientras aún está montada en el sistema.Esto elimina la necesidad de eliminar el chip para actualizaciones, reducir el tiempo de mantenimiento y mejorar la eficiencia.Puede implementar modificaciones de diseño sin interrumpir la producción, por lo que es una solución rentable para proyectos a largo plazo.

Rendimiento de alta velocidad

El dispositivo admite una alta frecuencia de operación interna de hasta 166.7 MHz, lo que permite un procesamiento rápido de datos y tiempos de respuesta.Esto lo hace ideal para aplicaciones que requieren procesamiento de señal, control lógico e interfaz de alta velocidad, asegurando una operación de sistema más suave y confiable.

Soporte de E/S versátil

Con hasta 68 pines de E/S configurables y compatibilidad con múltiples niveles de voltaje (3.3V, 5V y opciones tolerantes para 2.5V, 3.3V y 5V), el EPM7064STC100-7 ofrece flexibilidad en el diseño del sistema.Permite una integración perfecta en varios circuitos y admite entornos de voltaje mixto, reduciendo los problemas de compatibilidad con otros componentes.

Operación confiable en entornos

Diseñado para funcionar dentro de un rango de temperatura de 0 ° C a 70 ° C, el EPM7064STC100-7 garantiza un funcionamiento consistente y estable en una variedad de condiciones.Esta confiabilidad lo convierte en una opción preferida para aplicaciones donde se requiere estabilidad ambiental, como la automatización industrial, las telecomunicaciones y los sistemas de control integrados.

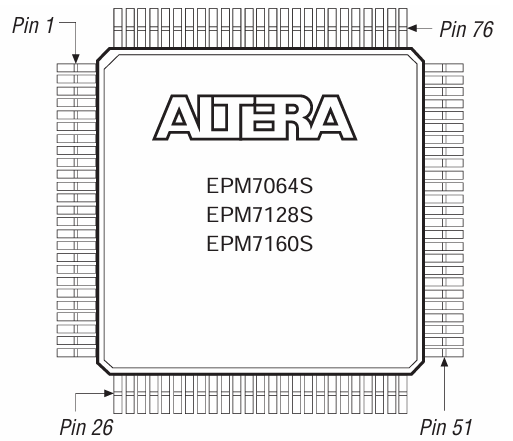

EPM7064STC100-7 Diagrama de pines de paquete

El EPM7064STC100-7 es un CPLD (dispositivo lógico programable complejo) de la serie Max 7000S de Altera, ubicada en un paquete plano quad delgado de 100 pines (TQFP-100).Este tipo de paquete está diseñado para aplicaciones de montaje en superficie, que ofrece un equilibrio de alta densidad de pasadores y tamaño compacto.El diagrama de pines Sigue un esquema de numeración en sentido antihorario, con el pin 1 ubicado en la esquina superior izquierda del paquete.Moviéndose en sentido antihorario, los primeros 25 alfileres ocupan el lado izquierdo, los pines 26 a 50 se colocan a lo largo del borde inferior, los pines 51 a 75 continúan a lo largo del lado derecho y los pasadores de 76 a 100 se distribuyen a lo largo del borde superior.El Paquete TQFP-100 Cuenta con cables delgados que se extienden hacia afuera desde los cuatro lados del cuerpo cuadrado plano.Este diseño mejora la compatibilidad de la monta de superficie mientras se mantiene un espacio adecuado para los pasadores para facilitar la soldadura y el ensamblaje.El paso de plomo (distancia entre pines adyacentes) típicamente es de 0.5 mm, optimizando la integridad de la señal al tiempo que minimiza la huella general.

EPM7064STC100-7 Fabricante

El EPM7064STC100-7 es un CPLD (dispositivo lógico programable complejo) desarrollado originalmente por Altera, una compañía de semiconductores conocida por sus soluciones lógicas programables.En 2015, Intel Adquirió Altera, integrando sus líneas de productos FPGA y CPLD en el grupo de soluciones programables (PSG) de Intel.Desde entonces, el EPM7064STC100-7 ha sido marcado bajo Intel, aunque se ha marcado como obsoleto.Intel, como fabricante, mantuvo el soporte heredado para los CPLD de la serie MAX® 7000S, incluido este modelo, al tiempo que cambia gradualmente su enfoque hacia FPGA modernas y tecnologías lógicas programables.

Conclusión

El EPM7064STC100-7 reúne funciones complejas, rendimiento rápido y actualizaciones fáciles en un chip, lo que demuestra su valor en las configuraciones digitales desafiantes.Esta guía ha demostrado cómo funciona, para qué se usa y cómo se ajusta a varios sistemas electrónicos.Ayuda a que los dispositivos funcionen sin problemas y eficientemente, lo que demuestra que todavía es muy útil para muchas aplicaciones.Esta guía proporciona una visión clara de cómo el EPM7064STC100-7 puede ayudar a mejorar los diseños electrónicos y las operaciones del sistema de manera efectiva.

Hoja de datos pdf

EPM7064STC100-7 Hojas de datos:

Acerca de nosotros

ALLELCO LIMITED

Lee mas

Consulta rápida

Envíe una consulta, responderemos de inmediato.

Preguntas frecuentes [FAQ]

1. ¿Cómo el retraso de propagación de 7.5ns del rendimiento de los circuitos de impacto EPM7064STC100-7?

Un retraso de propagación de 7.5ns garantiza el procesamiento de señal de baja latencia, lo que hace que este CPLD sea adecuado para aplicaciones de alta velocidad como el procesamiento de señales digitales (DSP), los sistemas de comunicación y la automatización industrial que requieren un control de tiempo preciso.

2. ¿Puede el EPM7064STC100-7 estar programado utilizando herramientas de desarrollo modernas?

Sí, se puede programar utilizando el software de Quartus II de Intel (anteriormente Altera Quartus) junto con un programador JTAG apropiado.Sin embargo, el soporte para CPLD más antiguos como el EPM7064STC100-7 puede estar limitado en las versiones de Quartus más nuevas, por lo que es posible que necesite usar versiones heredadas como Quartus II 13.0 SP1, que todavía admiten dispositivos MAX® 7000S Series.

3. ¿El EPM7064STC100-7 admite entornos de voltaje mixto?

Sí, admite niveles de lógica de 3.3V y 5V, lo que lo hace compatible con una amplia gama de circuitos digitales.Esta flexibilidad es útil para interfactar componentes Legacy 5V con sistemas modernos de 3.3V sin circuitos de cambio de nivel adicionales.

4. ¿Cuál es el mejor método para solucionar problemas de un diseño basado en EPM7064STC100-7?

Para solucionar problemas, puede usar el analizador lógico de Quartus SignalTap II o osciloscopios externos y analizadores lógicos para monitorear las señales.Si la depuración de problemas de programación JTAG, asegúrese de que las conexiones TDI, TDO, TCK y TMS sean correctas y que esté utilizando un programador USB Blaster o ByteBlasterMV compatible.

5. ¿Puedo programar el EPM7064STC100-7 sin eliminarlo de mi placa de circuito?

Sí.La programabilidad del sistema 5.0V (ISP) a través de JTAG (IEEE 1149.1) le permite reprogramar el dispositivo mientras permanece en el sistema.Esto hace que las actualizaciones de firmware, la depuración y las pruebas sean mucho más eficientes en comparación con los CPLD tradicionales.

Guía completa de la resistencia de 10k: código de color, aplicaciones y circuito usa el circuito

en 10/03/2025

Condensadores versus baterías: ¿Cuál es mejor para sus necesidades energéticas?

en 07/03/2025

Publicaciones populares

-

Computadoras de conjunto de instrucciones complejas: ¿Cómo cambiaron la informática?

en 18/04/8000 147770

-

USB-C Pinout y características

en 18/04/2000 112006

-

Uso de primitivas de simulación unificadas Xilinx: una guía completa para el diseño y simulación FPGA

en 18/04/1600 111351

-

Voltajes de fuente de alimentación en electrónica: significado de VCC, VDD, VEE, VSS y GND

en 18/04/0400 83768

-

Guía del conector RJ45: pinout, cableado, tipos de cables y usos

en 01/01/1970 79562

-

La mejor guía para los códigos de color de alambre en sistemas eléctricos modernos

La forma en que nuestros sistemas eléctricos usan colores no es solo para looks.Cada color de cable ahora indica una función específica, lo que hace que sea más fácil identificar y manejar componen...en 01/01/1970 66959

-

Guía de la válvula de purga: función, síntomas, pruebas y reemplazo para un rendimiento óptimo del motor

La válvula de purga es una parte clave del sistema de un automóvil que ayuda a mantener el aire limpio al administrar los vapores de combustible antes de que puedan escapar a la atmósfera.Esto no s...en 01/01/1970 63098

-

Factor de calidad (q): ecuaciones y aplicaciones

El factor de calidad, o 'Q', es importante al verificar qué tan bien funcionan los inductores y los resonadores en sistemas electrónicos que usan frecuencias de radio (RF).'Q' mide qué tan bien un ...en 01/01/1970 63040

-

Lograr el rendimiento máximo con el teorema de transferencia de potencia máxima

El teorema de transferencia de potencia máxima explica cómo la energía de una fuente, como una batería o generador, fluye a una carga conectada.Muestra la condición exacta en la que la carga recibe...en 01/01/1970 54096

-

A23 Especificaciones y compatibilidad de la batería

La batería A23 es una batería pequeña en forma de cilindro con alto voltaje.También llamado 23A, 23AE o MN21, funciona a 12 voltios y mucho más alto que las baterías AA o AAA.Su diseño esp...en 01/01/1970 52184