Todo lo que necesitas saber sobre DDR3

En el mundo de la tecnología de memoria en rápida evolución, DDR3 SDRAM se ha convertido en un avance innovador, abordando las crecientes demandas de eficiencia, rendimiento y escalabilidad en la informática moderna.Desde características innovadoras como el retraso de escritura de comandos (CWD) y en el motor de calibración de die (ODCE) hasta mejoras notables en la gestión de energía y el control térmico, DDR3 presenta una serie de capacidades que redefinen el rendimiento de la memoria.Este artículo explora las características clave, las mejoras arquitectónicas y las aplicaciones prácticas de DDR3, arrojando luz sobre cómo supera a su predecesor, DDR2, y establece un nuevo estándar en diseño de memoria para aplicaciones de consumidores e industriales.Catalogar

Descripción general

CWD, o retraso de escritura de comando, es un mecanismo diseñado para optimizar los retrasos en la escritura en los sistemas de memoria, mejorando la eficiencia de gestión de datos.El comando RESET activa un modo de ahorro de potencia súper en DDR3 SDRAM, deteniendo las operaciones de memoria y cambiando el sistema a reservas de baja energía.Esta característica conserva la energía y extiende la vida útil de la memoria, lo que la hace mayormente valiosa para aplicaciones móviles e integradas donde se utiliza la eficiencia energética.

La función ZQ avanza la calibración de resistencia del terminal a través del motor de calibración en el troquel (ODCE), ajuste fino en la resistencia de terminación del die (ODT) para mantener la integridad de la señal en condiciones variables.Esta calibración mitiga los riesgos como la degradación de la señal que puede comprometer la precisión de los datos y la estabilidad del sistema.Los entornos informáticos de alto rendimiento resaltan las mejoras de confiabilidad que proporcionan estas optimizaciones, especialmente en aplicaciones que exigen un rendimiento consistente.

La función de temperatura de autorreflash (SRT) integra el control de temperatura programable para los ajustes actuales a las velocidades de reloj de memoria en función de las condiciones térmicas.Esto mejora la gestión de energía y evita el sobrecalentamiento, un desafío común que puede conducir a una falla de estrangulamiento o componentes.Además, la característica de autorrefresh de la matriz parcial (PASR) actualiza selectivamente los segmentos de memoria activa, reduciendo significativamente el consumo de energía.Este enfoque dirigido para la gestión de recursos es ampliamente reconocido como una estrategia efectiva para optimizar el rendimiento de la memoria sin sacrificar la eficiencia, principalmente en sistemas con patrones de uso de memoria irregular.

Nuevo diseño de DDR3

La arquitectura de memoria DDR3 introduce un innovador diseño previo a la captura de 8 bits, que efectivamente duplica la característica previa de 4 bits anterior que se encuentra en DDR2.Este avance permite que el núcleo DRAM funcione a solo 1/8 de la frecuencia de datos.Por ejemplo, DDR3-800 opera a una frecuencia central de solo 100MHz, mostrando un salto significativo en eficiencia.

Las características clave de este diseño incluyen:

• La implementación de una topología punto a punto, que reduce significativamente la carga en la dirección, el comando y los buses de control, lo que lleva a un mejor rendimiento general del sistema.

• Un proceso de fabricación que cae por debajo de 100 nm, lo que resulta en una disminución en el voltaje de operación de 1.8V en DDR2 a 1.5V.Esta reducción no solo fomenta la eficiencia energética, sino que también promueve una mejor gestión térmica dentro del sistema.

• La introducción del reinicio asíncrono y las funcionalidades de calibración de ZQ, marcando una transformación significativa en el diseño que aumenta la estabilidad y la eficiencia operativa.

Estas mejoras reflejan un enfoque reflexivo para la arquitectura de la memoria, con el objetivo de satisfacer las demandas en evolución de la informática moderna al tiempo que considera aspectos como el consumo de energía y el rendimiento del sistema.

Comparación DDR2 y DDR3

|

Característica |

DDR2 |

DDR3 |

|

Longitud de explosión (BL) |

Bl = 4 se usa comúnmente |

Bl = 8 es fijo;Admite una ráfaga de 4 bits (BL = 4 Leer +

BL = 4 Escribir para sintetizar BL = 8).Controlado a través de la línea de dirección A12.Explosión

la interrupción está prohibida |

|

Dirección de tiempo |

Rango CL: 2–5;Rango de latencia adicional (AL): 0–4

|

Rango CL: 5–11;AL Opciones: 0, CL-1, CL-2.Agrega escritura

Retraso (CWD) basado en la frecuencia operativa |

|

Función de reinicio |

No disponible |

Recién introducido.Un pin de reinicio dedicado simplifica

inicialización, reduce el consumo de energía y detiene las funciones internas

durante el reinicio |

|

Calibración de zq |

No disponible |

Introducido con un pin Zq usando una referencia de 240 ohmios

resistor.Calibra automáticamente la salida de datos y la resistencia ODT |

|

Voltaje de referencia |

Voltaje de referencia única (VREF) |

Dividido en dos señales: vrefca (comando/dirección) y

VREFDQ (bus de datos), mejorando la relación señal / ruido |

|

Conexión punto a punto (P2P) |

Múltiples canales de memoria admitidos por controlador |

El controlador de memoria maneja un canal con una ranura,

habilitando relaciones P2P o P22P.Reduce la carga del bus y mejora

actuación |

|

Consumo de energía |

Mecanismos de autoinfresión estándar |

Características avanzadas como autoinfresh automático y parcial

Autofinfogo basado en la temperatura, lo que lleva a una mejor eficiencia |

|

Aplicaciones |

Utilizado principalmente en escritorios y servidores |

Ideal para dispositivos móviles, servidores y escritorios debido a

Alta frecuencia, velocidad y menor consumo de energía |

|

Soporte de plataforma futura |

Compatible con sistemas heredados y plataformas actuales |

Compatible con las plataformas de Intel's Bear Lake y AMD K9 para

compatibilidad futura |

Mejoras de memoria de DDR3

Bancos lógicos

La evolución de DDR2 a DDR3 representa un cambio notable en la arquitectura en memoria, iniciando con 8 bancos lógicos y el potencial de expandirse hasta 16. Este desarrollo va más allá de las mejoras técnicas;Refleja una demanda creciente de chips de alta capacidad capaces de manejar aplicaciones complejas.A medida que los requisitos de software y hardware continúan aumentando, la capacidad de admitir bancos más lógicos se vuelve cada vez más relevante.Las experiencias en varias industrias sugieren que los sistemas diseñados con escalabilidad en mente a menudo proporcionan mayores rendimientos a largo plazo, ya que pueden ajustarse a los cambios técnicos futuros sin la necesidad de revisiones extensas.

Embalaje

El empaque DDR3 significa un notable avance en la ingeniería, resaltado por un recuento de pin más alto que permite nuevas funcionalidades.La transición de los paquetes de FBGA de 68/68/84 bolas de DDR2 al FBGA de 78 bolas para chips de 8 bits y el FBGA de 96 bolas para chips de 16 bits ilustra este salto.Esta mejora no solo mejora las capacidades de transferencia de datos, sino que también refleja un creciente compromiso con la sostenibilidad, ya que DDR3 cumple con estrictos estándares ambientales, eliminando sustancias dañinas.En el panorama de fabricación actual, puede ser atraído cada vez más por los productos que priorizan la responsabilidad ecológica, enfatizando la necesidad de tejer prácticas sostenibles en innovaciones de alta tecnología.

Consumo de energía

Una característica destacada de DDR3 es su capacidad para ofrecer un alto ancho de banda mientras minimiza significativamente el consumo de energía.Al reducir el voltaje operativo de 1.8V de DDR2 a 1.5V, se prevé que DDR3 use un 30% menos de potencia en general.Las relaciones de potencia para DDR3-800, 1066 y 1333—0.72x, 0.83x y 0.95x respectivamente, evitan una ruta clara hacia un mayor rendimiento y eficiencia.Esta disminución en el consumo de energía no solo respalda la sostenibilidad ambiental, sino que también prolonga la vida útil del dispositivo, ya que la generación de calor reducida conduce a menos estrés térmico en los componentes.Los datos históricos de varios sectores indican que las tecnologías de eficiencia energética tienden a reducir los costos operativos con el tiempo, lo que refuerza el valor de DDR3.

Pros en el rendimiento

|

Ventaja de rendimiento |

Detalles |

|

Menos consumo de energía y calor |

DDR3 dibuja lecciones de DDR2, reduciendo el consumo de energía

y calor mientras mantiene el control de costos.Esto hace que DDR3 te sea más atractivo |

|

Mayor frecuencia de operación |

Debido al menor consumo de energía, DDR3 logra más alto

operaciones de frecuencias, compensar por tiempos de retraso más largos y servir como un

punto de venta para tarjetas gráficas |

|

Costo de tarjeta gráfica reducida |

DDR3 utiliza partículas de memoria más grandes (32 m x 32 bits),

Requerir menos chips para lograr la misma capacidad que DDR2, reduciendo PCB

área, consumo de energía y costo |

|

Versatilidad mejorada

|

DDR3 ofrece una mejor compatibilidad con DDR2 debido a

Características clave sin cambios (pines, embalaje), lo que permite una integración más fácil con

Diseños DDR2 existentes |

|

Amplia adopción |

DDR3 se usa ampliamente en nuevas tarjetas gráficas de alta gama y

cada vez más adoptado en tarjetas gráficas de gama baja |

Historia de crecimiento

El estándar de memoria DDR3, presentado oficialmente por JEDEC el 28 de junio de 2002, representó un momento importante en la evolución de la tecnología de memoria.Sin embargo, no fue sino hasta 2006 que DDR2 realmente comenzó a forjar su nicho en el mercado.Este retraso en la aceptación generalizada no disuadió a los fabricantes de buscar ansiosamente soluciones DDR3, destacando un enfoque visionario de la tecnología de memoria que finalmente transformaría la industria.

Cuota de mercado

Los analistas del mercado, incluidos los de Isuppli, anticiparon que para 2008, DDR3 establecería una posición dominante dentro del sector de la memoria, pronosticando una cuota de mercado del 55%.Para el cierre de 2008, los módulos de memoria DDR3, que operan a frecuencias de 1066, 1333 y 1600 MHz, se pusieron fácilmente disponibles para los consumidores.Si bien DDR3 compartió similitudes arquitectónicas con DDR2, abordó efectivamente las deficiencias de su predecesor, facilitando una transición más suave y fomentando una aceptación más amplia.Esta progresión ilustra el valor de la flexibilidad en los avances técnicos, ya que puede responder con precisión a las necesidades del consumidor al tiempo que mejora las métricas de rendimiento.

Nuevas características

La memoria DDR3 trae mejoras sustanciales sobre DDR2, con tasas de transferencia de datos elevadas, una topología innovadora para los autobuses de dirección y control, y una mejor eficiencia energética.La introducción de un diseño previo de 8 bits combinado con una arquitectura punto a punto no solo optimiza las operaciones sino que también eleva el rendimiento general.Estas mejoras reflejan una tendencia más amplia en tecnología donde la velocidad y la eficiencia reinan supremos.Las ideas de varios sectores revelan que aquellos que adoptan la innovación a menudo aseguran una ventaja competitiva, evidenciada por la rápida adopción de DDR3 en múltiples aplicaciones.

Hito

A fines de 2009, Samsung captó la atención con la liberación de un innovador chip DDR3 de 4 GB fabricado usando un proceso de 50 nm, lo que permite la creación de palos de memoria de 32 GB y mejorando significativamente el potencial de la computación de 64 bits.Este chip también contó con una impresionante reducción del 40% en el consumo de energía en comparación con las generaciones anteriores.Las proyecciones que indican un aumento en la participación de mercado de DDR3 al 72% para 2011 acentuaron aún más la progresión natural de DDR2 a DDR3.Este cambio sirve como un recordatorio de la naturaleza cíclica del avance tecnológico, donde cada nueva iteración se basa en su predecesor, impulsando la innovación y la eficiencia en un entorno digital en constante cambio.

Acerca de nosotros

ALLELCO LIMITED

Lee mas

Consulta rápida

Envíe una consulta, responderemos de inmediato.

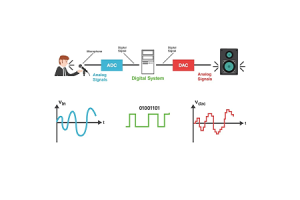

Procesamiento de señal digital: principios y aplicaciones

en 30/12/2024

Explorando Bloque RAM en la serie Xilinx SP3: características, diferencias y optimización

en 30/12/2024

Publicaciones populares

-

Computadoras de conjunto de instrucciones complejas: ¿Cómo cambiaron la informática?

en 18/04/8000 147757

-

USB-C Pinout y características

en 18/04/2000 111936

-

Uso de primitivas de simulación unificadas Xilinx: una guía completa para el diseño y simulación FPGA

en 18/04/1600 111349

-

Voltajes de fuente de alimentación en electrónica: significado de VCC, VDD, VEE, VSS y GND

en 18/04/0400 83721

-

Guía del conector RJ45: pinout, cableado, tipos de cables y usos

en 01/01/1970 79508

-

La mejor guía para los códigos de color de alambre en sistemas eléctricos modernos

La forma en que nuestros sistemas eléctricos usan colores no es solo para looks.Cada color de cable ahora indica una función específica, lo que hace que sea más fácil identificar y manejar componen...en 01/01/1970 66910

-

Guía de la válvula de purga: función, síntomas, pruebas y reemplazo para un rendimiento óptimo del motor

La válvula de purga es una parte clave del sistema de un automóvil que ayuda a mantener el aire limpio al administrar los vapores de combustible antes de que puedan escapar a la atmósfera.Esto no s...en 01/01/1970 63046

-

Factor de calidad (q): ecuaciones y aplicaciones

El factor de calidad, o 'Q', es importante al verificar qué tan bien funcionan los inductores y los resonadores en sistemas electrónicos que usan frecuencias de radio (RF).'Q' mide qué tan bien un ...en 01/01/1970 63012

-

Lograr el rendimiento máximo con el teorema de transferencia de potencia máxima

El teorema de transferencia de potencia máxima explica cómo la energía de una fuente, como una batería o generador, fluye a una carga conectada.Muestra la condición exacta en la que la carga recibe...en 01/01/1970 54081

-

A23 Especificaciones y compatibilidad de la batería

La batería A23 es una batería pequeña en forma de cilindro con alto voltaje.También llamado 23A, 23AE o MN21, funciona a 12 voltios y mucho más alto que las baterías AA o AAA.Su diseño esp...en 01/01/1970 52127