D Flip-flop: ¿Cómo funciona y dónde se usa?

La electrónica digital forma la columna vertebral de la tecnología moderna, y en su corazón se encuentra el flip-flop, un componente serio en el almacenamiento de datos y los circuitos secuenciales.Este dispositivo versátil captura y preserva los datos con precisión, asegurando un flujo de información suave a través de aplicaciones que van desde circuitos de conteo básicos hasta máquinas de estado complejas.En este artículo, profundizaremos en la arquitectura, la funcionalidad y la importancia real del flip-flop, descubriendo cómo su diseño robusto facilita el manejo de datos confiable incluso en los sistemas digitales más exigentes.Únase a nosotros mientras exploramos los principios y las aplicaciones prácticas de este componente de construcción requerido en la lógica digital.Catalogar

Descripción general de la flip-flop

El Flip-Flop D se erige como una piedra angular en la electrónica digital, actuando como un dispositivo de almacenamiento dinámico para la información.Su papel se acentúa por la capacidad de mantener un estado estable, representado por los dígitos binarios "0" y "1."Esta característica permite que el flip-flop D funcione como un bloque de construcción final para varios circuitos secuenciales.La operación de este dispositivo no es simplemente un tecnicismo;Encarna la esencia de las aplicaciones lógicas digitales, lo que permite transiciones suaves entre los estados cuando se desencadena por una señal externa.

La arquitectura de las chanclas D comprende una combinación de chanclas integradas y circuitos de puerta.Este diseño les permite operar en dos modos principales: activado por nivel y activado por el borde.Las chanclas activadas por nivel se activan cuando el pulso del reloj (CP) es alto, mientras que las flipps activadas por el borde están específicamente sintonizadas con el borde ascendente de la señal CP.Esta diferenciación proporciona un marco para el control preciso sobre el almacenamiento y la recuperación de datos, asegurando que cada bit de información se trate con la máxima atención.El estado de salida de un flip-flop d está determinado por la entrada D justo antes de activar, lo que facilita las operaciones como configurar la salida en "0" o "1."En los modelos activados por el borde, las alteraciones a la entrada D durante el alto estado de CP siguen siendo intrascendentes para la salida, salvaguardando así la integridad y confiabilidad de los datos.

La adaptabilidad de las flip-flops es evidente en sus amplias aplicaciones dentro de los sistemas digitales.Desempeñan un papel importante en la operación de registros, registros de cambio y divisores de frecuencia, entre otros.La aplicación de flip-flops se puede observar en una variedad de tecnologías, que abarca desde relojes digitales básicos hasta microprocesadores sofisticados.Por ejemplo, en la arquitectura de un registro de turno, las chanclas D facilitan el movimiento secuencial de los bits de datos, lo que permite una manipulación y almacenamiento de datos efectivos.Esta flexibilidad resalta la importancia de comprender los principios operativos de las chanclas D, ya que sientan las bases para elaborar circuitos digitales resistentes.

Estructura de D Flip-flop

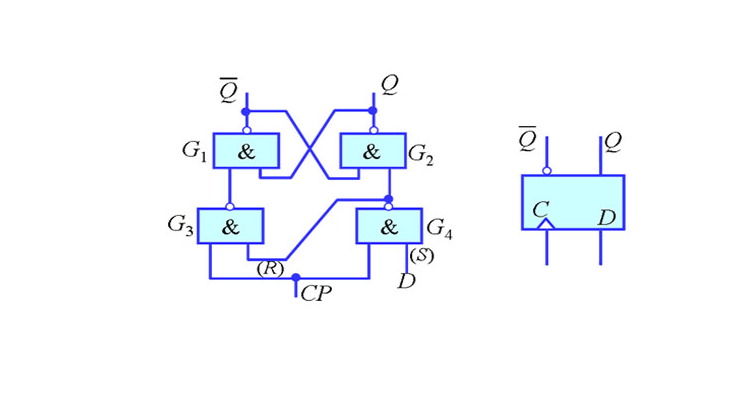

El Flip-flop D sirve como base en la electrónica digital, creada a partir de un cuarteto de puertas de NAND.Dentro de este intrincado marco, las Gates G1 y G2 unen fuerzas para establecer la mejor configuración de flip-flop RS.

• Desencadenado: En los diseños activados por nivel, se vuelve útil para que las señales de entrada permanezcan estables antes del borde positivo del pulso del reloj.Cualquier fluctuación o perturbación durante este intervalo principal puede conducir a estados no intencionados y erróneos dentro del flip-flop, lo que puede causar interrupciones notables en la operación de un sistema digital más grande.Este escenario enfatiza la naturaleza seria de la integridad y el momento de la señal en los circuitos digitales, ya que incluso las más mínimas perturbaciones pueden la bola de nieve en errores considerables.

• Activado por el borde : Los diseños activados por el borde presentan una alternativa más resistente.Estas configuraciones permiten aplicar las entradas justo antes del borde del reloj, disminuyendo así las posibilidades de perturbaciones que afectan el estado de salida.Dicha característica resulta principalmente beneficiosa en sistemas intrincados donde convergen múltiples señales, ofreciendo una mayor flexibilidad y confiabilidad en el tiempo.A menudo se conoce como flip-flops de borde de bloqueo de sostenimiento, se pueden diseñar vinculando dos chanclas D en serie.En esta configuración, el pulso del reloj para el primer flip-flop se invertida utilizando una puerta no, lo que resulta en una condición en la que el segundo flip-flop se activa solo en el borde que cae de la señal del reloj.Este enfoque no solo refuerza la estabilidad de la salida, sino que también allana el camino para elaborar circuitos secuenciales más complejos.

Principio de trabajo de D Flip-flop

El flip-flop RS se basa en un concepto final de retención estatal, que juega un papel sustancial en los circuitos digitales.Recibe entradas de terminales preestablecidos (SD) y Clear (RD), que se activan a niveles bajos.

• Cuando SD es alto y RD es bajo, el flip-flop se ve forzado a un estado "0", independientemente de la entrada D.

• Igualmente, cuando SD es bajo y RD es alto, la flip-flop pasa a un estado "1".

• Si ambas entradas son altas, el circuito permanece sin cambios, resaltando cómo las condiciones de entrada dictan el comportamiento del flip-flop.

En situaciones donde el pulso del reloj (CP) es bajo, las puertas G3 y G4 permanecen inactivas, preservando el estado actual del flip-flop.El mecanismo de retroalimentación de Q3 y Q4 es imprescindible, lo que permite que la entrada D se registre como Q5 y Q6.Las transiciones de flip-flop ocurren en el borde ascendente de CP, activando G3 y G4.Las salidas de estas puertas están directamente influenciadas por los estados de G5 y G6, mostrando una clara dependencia de las condiciones anteriores.Una vez que el flip-flop cambia el estado, la entrada se bloquea de manera efectiva durante la fase alta de CP, evitando cualquier cambio adicional hasta el siguiente borde del reloj.

Este mecanismo de retroalimentación tiene un doble propósito: no solo garantiza que el flip-flop conserve su estado, sino que también establece líneas específicas para establecer y bloquear los estados.Este diseño permite la aceptación de las entradas antes del borde del reloj mientras se activa simultáneamente en el borde, evitando así cualquier entrada posterior.Las chanclas activadas por el borde, en particular, ofrecen una resistencia mejorada a la interferencia y demuestran velocidades operativas más rápidas en comparación con las configuraciones tradicionales de esclavo maestro.Esta mejora proviene de su capacidad para responder a los bordes del reloj en lugar de los niveles, lo que reduce el riesgo de cambios de estado erróneos causados por fluctuaciones de ruido o señal.

D Características del pulso de flip-flop

Tiempo de configuración

Para lograr un máximo rendimiento en los circuitos digitales, los estados de salida de las puertas G5 y G6 deben estabilizarse antes de que ocurra el borde ascendente del pulso del reloj (CP).La señal de entrada en el terminal D debe llegar antes de este borde del reloj, lo que se adhiere a la condición de tiempo de configuración de la tumba: tset ≥ 2tpd.Este principio destaca la importancia del tiempo dentro de los sistemas sincrónicos, donde incluso las discrepancias de tiempo ligeras pueden conducir a un comportamiento errático.En las aplicaciones, a menudo puede participar en análisis de tiempo integrales para verificar que se cumplan los requisitos de tiempo de configuración, que a su vez refuerza la confiabilidad del sistema.

Tener tiempo

El desencadenamiento de borde juega un papel importante en el diseño de circuitos sincrónicos, lo que requiere que la salida de la puerta G5 permanezca estable durante el alto estado de la PC.Específicamente, cuando d = 0, la salida de bajo nivel de la puerta G3 debe estabilizarse antes de que ocurran cambios en el terminal D.Por lo tanto, el tiempo de retención para una señal de bajo nivel se define como THL ≥ TPD.Por otro lado, para d = 1, el tiempo de retención es THH = 0, ya que la salida de G4 bloquea efectivamente G3 después del borde ascendente de CP.

Tiempo de retraso de transmisión

Con la llegada del borde de aumento de CP, los tiempos de retraso de salida se caracterizan como TPHL para transiciones de alta a baja y TPLH para transiciones de bajo a alto, con valores designados de TPHL = 3TPD y TPLH = 2TPD.Estos retrasos representan las características de propagación inherentes de las puertas involucradas.En la práctica, puede utilizar con frecuencia herramientas de simulación para modelar con precisión estos retrasos, lo que permite ajustes que pueden abordar posibles problemas de tiempo dentro de los circuitos complejos.La capacidad de prever y tener en cuenta los retrasos en la transmisión es una marca registrada de un diseño digital efectivo, ya que afecta directamente el rendimiento y la confiabilidad del sistema.

Frecuencia de reloj máxima

Para garantizar una operación confiable del flip-flop síncrono RS, la duración del alto nivel CP debe superar a TPHL, lo que significa que el ancho del reloj TWH debe ser mayor que TPHL.Además, el bajo nivel del reloj no debe ser más corto que el total del retraso de la transmisión de la puerta G4 y el tiempo de configuración: TWL ≥ TSET + TPD.Esta relación entre la frecuencia del reloj y los parámetros de tiempo es notable;A menudo puede encontrar el desafío de equilibrar la velocidad con la confiabilidad.En diseños integrados, las variaciones en el tiempo de transmisión a través de las puertas pueden complicar las cosas, lo que lleva a evaluaciones cualitativas que requieren validación empírica.

En el diseño digital, dirigirse a los sesgos del árbol del reloj es grave, ya que afectan significativamente la precisión de la sincronización.Las simulaciones generalmente usan retrasos máximos para las verificaciones de configuración y retrasos mínimos para las evaluaciones de tiempo de retención, asegurando que se cumplan todas las limitaciones de tiempo para un diseño robusto.Las restricciones de tiempo de configuración se relacionan con los ciclos de reloj, donde la reducción de la frecuencia del reloj puede mejorar la funcionalidad si las frecuencias altas no son prácticas.En contraste, el tiempo de retención es independiente de los ciclos de reloj, y el mal diseño o enrutamiento puede degradar el rendimiento independientemente de los ajustes de frecuencia del reloj.Un enfoque integral para el diseño de temporización, principalmente en dispositivos programables, es dinámico para administrar las inclinaciones del árbol del reloj y garantizar la confiabilidad y el rendimiento del sistema.

Acerca de nosotros

ALLELCO LIMITED

Lee mas

Consulta rápida

Envíe una consulta, responderemos de inmediato.

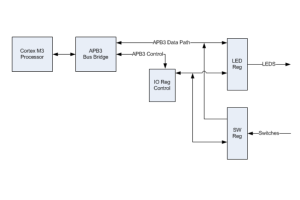

MMIO explicó: ¿Cómo funciona y por qué importa?

en 27/12/2024

4N25 OptoCoupler: características, pinout y equivalentes

en 27/12/2024

Publicaciones populares

-

Computadoras de conjunto de instrucciones complejas: ¿Cómo cambiaron la informática?

en 08/05/8000 147969

-

USB-C Pinout y características

en 08/05/2000 118955

-

Uso de primitivas de simulación unificadas Xilinx: una guía completa para el diseño y simulación FPGA

en 08/05/1600 111530

-

Voltajes de fuente de alimentación en electrónica: significado de VCC, VDD, VEE, VSS y GND

en 08/05/0400 86988

-

Guía del conector RJ45: pinout, cableado, tipos de cables y usos

en 01/01/1970 84360

-

La mejor guía para los códigos de color de alambre en sistemas eléctricos modernos

La forma en que nuestros sistemas eléctricos usan colores no es solo para looks.Cada color de cable ahora indica una función específica, lo que hace que sea más fácil identificar y manejar componen...en 01/01/1970 69092

-

Factor de calidad (q): ecuaciones y aplicaciones

El factor de calidad, o 'Q', es importante al verificar qué tan bien funcionan los inductores y los resonadores en sistemas electrónicos que usan frecuencias de radio (RF).'Q' mide qué tan bien un ...en 01/01/1970 65804

-

Guía de la válvula de purga: función, síntomas, pruebas y reemplazo para un rendimiento óptimo del motor

La válvula de purga es una parte clave del sistema de un automóvil que ayuda a mantener el aire limpio al administrar los vapores de combustible antes de que puedan escapar a la atmósfera.Esto no s...en 01/01/1970 64665

-

Lograr el rendimiento máximo con el teorema de transferencia de potencia máxima

El teorema de transferencia de potencia máxima explica cómo la energía de una fuente, como una batería o generador, fluye a una carga conectada.Muestra la condición exacta en la que la carga recibe...en 01/01/1970 54879

-

A23 Especificaciones y compatibilidad de la batería

La batería A23 es una batería pequeña en forma de cilindro con alto voltaje.También llamado 23A, 23AE o MN21, funciona a 12 voltios y mucho más alto que las baterías AA o AAA.Su diseño esp...en 01/01/1970 54080